Allied Scientific Pro (ASP) a développé et fabriqué un système de test laser SEE. Offrant un contrôle total sur un large éventail de paramètres, il permet des tests précis.

Forte d'une longue expertise en nano-usinage laser et en micro-usinage, ASP est en mesure de proposer un système SEE commercial répondant aux besoins du marché des semi-conducteurs. Compact et robuste, notre système laser offre une longue durée de vie et une maintenance réduite, voire inexistante, pendant des années. Nous utilisons les dernières technologies laser et scanner pour garantir des performances de haute qualité et des tests rapides.

Les services de laboratoire laser ASP peuvent aider les scientifiques en établissant des paramètres optimaux à partir d'échantillons fournis si nécessaire.

Nous proposons des solutions de test laser SEE personnalisées ;

- Photon unique (SPA) 1030 nm

- Deux photons (TPA) 1260 nm ou 1240 nm, ou 1340 nm

- Large bande interdite pour laser femtoseconde SiC et GaN 700-800 nm

- Double mode disponible

- Sélection de lasers Pico et Femtoseconde

- Système d'imagerie à ondes courtes de 900 nm à 1700 nm et visible, VGA ou HD

- Choix d'objectifs de microscope ; 200X, 100X, 50X 20X

- Configuration personnalisée pour répondre à tous les budgets

- En option : station de gaufrettes

Caractéristiques supplémentaires :

- Platines motorisées X-Y-Z de haute précision (résolution nm) Course XYZ de 50 mm, résolution de 0,1 micron

- Joystick pour X-Y

- Tilt stat (3 axes de rotation) micromètre manuel ou motorisé

- Enceinte de protection

- Objectif de microscope double en haut et en bas (en option)

- Remplacer le temps et le coût élevé de la ligne de faisceau synchrotron

- Pour l'espace, l'armée, l'aérospatiale, les chemins de fer, l'automobile, l'avionique

Applications :

- SEU : test de perturbation d'événement unique dans les circuits intégrés numériques et analogiques

- SET : Transitoire à événement unique dans les circuits intégrés linéaires et RF

- SEL : dépistage et localisation du verrouillage d'événement unique pour les COTS

- SEB : Burnout à événement unique dans les appareils électriques

- SEFI : interruption fonctionnelle à événement unique

Autres types de tests possibles avec laser :

Effet photoélectrique :

- OBIC (courant induit par faisceau optique)

- Injection de défauts − LADA (Laser Assisted Device Alteration)

- LIVA (Modification de la tension induite par la lumière)

Effet photothermique :

- OBIRCh (Changement de résistance induit par faisceau optique)

- TIVA (altération de tension induite thermiquement)

Type de tests :

- Essais d'effet des radiations

- Analyse des échecs

- Injection de défauts

- Stimulation laser photoélectrique

- Stimulation laser photothermique

Principaux avantages :

- Le laser peut cibler une zone spécifique de votre dispositif IC avec une précision de 50 nm ou moins

- Le système laser peut être à votre disposition dans votre propre laboratoire

- Accès facile et coût de déplacement réduit

- Aidez à accélérer vos choix de produits COTS (produits commerciaux prêts à l'emploi)

- Aidez à préserver la propriété intellectuelle et les secrets commerciaux en interne

Modèles compatibles :

- FPGA

- SRAM

- CMOS

- NMOS

- MOSFET

- Beaucoup d'autres

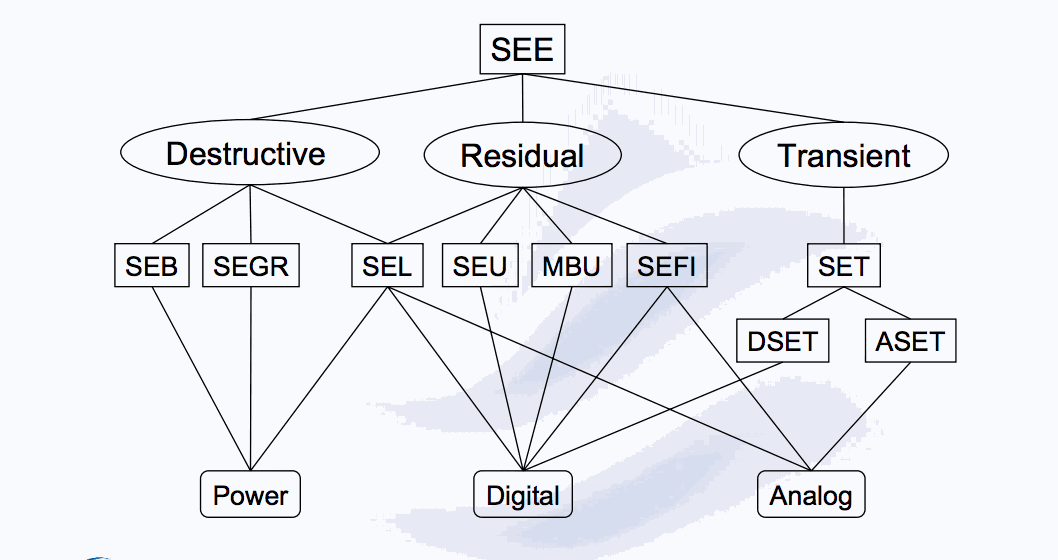

Effet d'événement unique (EES) : tout changement mesurable ou observable de l'état ou des performances d'un dispositif, d'un composant, d'un sous-système ou d'un système microélectronique (numérique ou analogique) résultant d'un impact d'une seule particule énergétique.

Transitoire à événement unique (SET) : erreur logicielle causée par le signal transitoire induit par l'impact d'une seule particule énergétique.

Verrouillage d'événement unique (SEL) : état de courant élevé anormal dans un composant, causé par le passage d'une seule particule énergétique à travers des zones sensibles de la structure du composant, et entraînant la perte de fonctionnalité du composant. Le SEL peut endommager définitivement le composant. Si le composant n'est pas endommagé de manière permanente, un cycle d'alimentation (mise hors tension puis sous tension) est nécessaire pour rétablir un fonctionnement normal. Un exemple de SEL dans un composant CMOS est lorsque le passage d'une seule particule induit la création d'un court-circuit bipolaire parasite (p-n-p-n) de l'alimentation à la terre. Section efficace de verrouillage d'événement unique (SEL) : nombre d'événements par unité de fluence. Pour la section efficace de SEL d'une puce, les dimensions sont de cm² par puce.

Si la charge générée par une seule particule à TLE élevé est collectée par un nœud sensible du dispositif ou du circuit, et que cette charge est supérieure à la charge critique requise pour initier un comportement anormal, un effet, même uniforme, peut affecter les performances électriques du dispositif ou du circuit, comme des erreurs logicielles ou des erreurs destructives graves. Les systèmes spatiaux nécessitent souvent des composants électroniques capables de fonctionner dans un environnement à fort rayonnement. Ce rayonnement peut provenir de particules piégées dans les champs magnétiques planétaires (par exemple, les ceintures de Van Allen qui affectent les satellites en orbite terrestre ou les champs de rayonnement intenses de Jupiter et de ses lunes), des rayons cosmiques galactiques ou des protons de haute énergie issus d'événements solaires. En orbite terrestre basse, un circuit intégré peut être exposé à quelques kilorads de rayonnement au cours de sa durée de vie utile, tandis qu'en orbite au milieu des ceintures de Van Allen, les niveaux d'exposition peuvent atteindre plusieurs centaines de kilorads, voire plus. Outre l'environnement spatial naturel, les satellites militaires doivent pouvoir survivre à des sursauts de rayonnement transitoires résultant d'une explosion nucléaire hostile. Pour atteindre ces niveaux supérieurs, des circuits intégrés résistants aux radiations sont nécessaires. En général, ces circuits sont fabriqués selon des procédés et des conceptions spécialisés qui augmentent considérablement leur tolérance aux rayonnements ionisants.

Défaillances des semi-conducteurs

Les principaux effets du rayonnement spatial naturel sur l'électronique des engins spatiaux sont la dose ionisante totale (DIT) et les effets d'événement unique (EES). Le DIT crée une charge d'oxyde en vrac et une charge de piégeage d'interface qui réduisent le gain du transistor et modifient les propriétés de fonctionnement (par exemple, la tension de seuil) des semi-conducteurs. L'accumulation de DIT entraîne la défaillance d'un dispositif si (1) la tension de seuil du transistor se décale suffisamment pour provoquer un dysfonctionnement du circuit, (2) le dispositif ne fonctionne pas à la fréquence requise et/ou (3) l'isolation électrique entre les dispositifs est rompue. L'EES se produit lorsqu'un rayon cosmique ou une autre particule de très haute énergie frappe un dispositif. La particule génère une traînée dense de paires électron-trou lors de son passage à travers le semi-conducteur, et ces porteurs libres sont collectés aux jonctions dopantes. Il en résulte une perturbation du circuit et un risque de perte de données (appelé « single-event-unlease » ou SEU). Le passage d'une particule suffisamment énergétique à travers une zone critique d'un composant peut même entraîner une défaillance définitive d'un circuit intégré (CI) en raison d'un blocage par événement de particule unique (SEL), d'un grillage ou d'une rupture diélectrique/de grille. En général, les composants présentant un SEL ne sont pas acceptables pour les applications spatiales, sauf si le blocage peut être détecté et atténué. Le grillage et la rupture de grille sont particulièrement problématiques pour l'électronique haute tension et/ou courant élevé associée aux alimentations spatiales. Les SEE sont devenus une préoccupation croissante à mesure que les CI utilisent des géométries de composants plus petites et des tensions de fonctionnement plus basses, ce qui entraîne une réduction de la capacité nodale et de la charge stockée sur les nœuds du circuit. Outre ces effets primaires, les dommages par déplacement causés par les protons et les électrons à haute énergie peuvent réduire la durée de vie des missions en raison des dommages à long terme causés aux CCD, à l'optoélectronique et aux cellules solaires.

Radioprotection

La technologie durcie aux radiations est souvent caractérisée comme une technologie pour laquelle le fabricant a pris des mesures spécifiques (c.-à-d. des contrôles) au niveau des matériaux, des procédés et de la conception afin d'améliorer la résistance aux radiations d'une technologie commerciale. Prenons l'exemple de la technologie CMOS, dont les faibles exigences en termes de puissance et de tension en font un candidat privilégié pour les applications spatiales. Le mécanisme de défaillance le plus probable des dispositifs CMOS résultant de la TID est une perte d'isolation causée par des fuites parasites entre la source et le drain du dispositif. Pour améliorer la résistance aux radiations, des modifications de la structure d'isolation peuvent être nécessaires, par exemple la formation d'une zone fortement dopée, ou « bande de garde », par implantation ionique, qui bloque efficacement les fuites parasites induites par les radiations. De plus, un faible budget thermique et une quantité minimale d'hydrogène pendant le traitement se sont avérés améliorer la résistance aux radiations. L'utilisation de transistors surdimensionnés et de résistances de contre-réaction, de condensateurs ou de transistors peut être mise en œuvre pour améliorer l'immunité aux radiations. Pour améliorer le verrouillage et l'immunité transitoire, le changement peut parfois être aussi simple que l'utilisation d'un substrat épitaxial mince. La technologie SOI, qui utilise une couche active construite sur un substrat isolant, peut (avec une conception appropriée) améliorer considérablement la SEE et la tolérance transitoire. Plusieurs approches de conception permettent également d'accroître la résistance aux radiations. Une modification de conception globale consiste à convertir les circuits dynamiques en un fonctionnement entièrement statique, plaçant ainsi les données dans une configuration plus stable et moins sensible aux effets perturbateurs des radiations. Pour le TID, les transistors à canal N peuvent être conçus en géométrie « fermée » qui bloque les chemins de fuite parasites. Pour le SEU, les cellules mémoire avec transistors supplémentaires peuvent assurer la redondance et le codage correcteur d'erreurs (ECC) pour identifier et corriger les erreurs. Les approches de conception visant à améliorer la résistance aux radiations entraînent généralement une baisse des performances et de la surface de routage. Sauf mesures spécifiques telles que celles-ci lors de la conception et de la fabrication d'un composant, les niveaux de résistance aux radiations sont généralement faibles et variables.

Non durci aussi

Les circuits CMOS commerciaux non renforcés sont généralement capables de supporter des niveaux de TID compris entre 5 et 30 kilorads à des débits de dose comparables à ceux de l'espace. (L'unité de TID couramment utilisée est le rad, c'est-à-dire la dose de rayonnement absorbée. Un rad équivaut à une énergie adsorbée de 100 ergs par gramme de matériau.) Cependant, de nombreuses missions spatiales peuvent utiliser la technologie CMOS commerciale. Lors de ces missions (par exemple, en orbite terrestre basse), le vaisseau spatial peut n'être exposé qu'à quelques kilorads de TID au cours de sa durée de vie. À titre d'exemple, la station spatiale Freedom peut nécessiter des circuits intégrés dont les exigences de renforcement varient de quelques kilorads à 20 kilorads selon l'emplacement de la plateforme. Dans ces applications, le blindage et un contrôle rigoureux de la technologie (afin de tirer parti du recuit en environnement spatial) permettent l'utilisation de certaines technologies commerciales non renforcées. Historiquement, les circuits bipolaires ont été très tolérants à la dose ionisante totale. Récemment, les avancées majeures de la technologie bipolaire sont dues en partie à l'introduction des « oxydes encastrés ». L'isolation diélectrique latérale de ces oxydes agit comme un arrêt de diffusion et minimise les capacités de jonction. Ainsi, les oxydes encastrés permettent des dimensions de caractéristiques bien plus petites, une densité de remplissage accrue et une vitesse plus élevée. Cependant, une fois irradiés, plusieurs chemins de fuite parasites peuvent se former, notamment une canalisation entre couches enterrées, une canalisation entre collecteurs et émetteurs sur les émetteurs à parois, et une augmentation du courant latéral. L'augmentation du courant associée à l'inversion de ces transistors MOS à effet de champ parasites peut entraîner une défaillance des circuits bipolaires à des doses aussi faibles que 10 kilorads. Bien que la technologie bipolaire offre des avantages en termes de vitesse, sa consommation énergétique relativement élevée la rend moins intéressante que le CMOS pour la plupart des applications spatiales. Ces dernières années, certains circuits bipolaires ont montré une sensibilité accrue aux faibles débits de dose, ce qui se traduit par une tolérance aux rayonnements plus faible pour les dispositifs à des débits de dose similaires à ceux observés dans l'espace, par rapport aux résultats des tests en laboratoire à débits de dose plus élevés. Les circuits CMOS sont généralement les moins sensibles au SEU en raison de la présence de composants actifs qui rétablissent le niveau de tension d'origine d'un nœud après une transitoire de tension induite par un impact d'ions lourds. De par leur faible consommation d'énergie, les circuits CMOS sont souvent le choix idéal pour les applications spatiales. Cependant, les SRAM CMOS non renforcées peuvent subir des perturbations à un taux de 10-5 à 10-3 erreurs/(bit-jour), ce qui représente une perturbation toutes les heures pour un satellite avec un grand élément de mémoire en orbite terrestre basse qui traverse l'anomalie de l'Atlantique Sud, une zone de densité de protons exceptionnellement élevée qui recouvre une grande partie de l'Amérique du Sud et de l'océan Atlantique Sud.

Sensibilité DRAM

Les circuits dynamiques sont généralement très sensibles à la SEU et ne sont pas utilisés dans les applications spatiales critiques. Dans les circuits dynamiques, tels que les DRAM (mémoires vives dynamiques) et les CCD (dispositifs à couplage de charge), l'information est représentée par la charge stockée sur un nœud du circuit. Dans les DRAM, cette charge s'échappe progressivement du nœud de stockage et doit être rafraîchie périodiquement. Une perturbation se produit dans ces dispositifs si une charge suffisante est collectée sur un nœud touché pour compenser la charge stockée d'origine. Bien que les DRAM et les CCD ne soient pas recommandés pour les applications de circuits critiques, ils sont de plus en plus utilisés dans les enregistreurs de données à semi-conducteurs et les systèmes d'imagerie où une ECC robuste peut restaurer les données corrompues. Les dispositifs bipolaires sont généralement moins sensibles à la SEU que les circuits dynamiques, mais plus sensibles que les dispositifs MOS. Les dispositifs bipolaires dépendent du pilotage du courant dans le circuit plutôt que du stockage de charge pour représenter l'état binaire des éléments mémoire. Il existe plusieurs zones de collecte de charge associées aux régions d'émetteur, de base, de collecteur et de substrat des transistors, et chacune de ces zones peut avoir une charge critique différente pour la perturbation. Dans certaines zones, comme les bases des transistors, la charge est amplifiée par le fonctionnement normal du dispositif. Un seul ion peut pénétrer plusieurs zones sensibles, ce qui entraîne des effets synergétiques entre les mécanismes de perturbation de chaque zone. L'environnement radiatif spatial naturel représente un défi majeur pour les systèmes satellitaires actuels et futurs disposant d'importantes ressources spatiales. Définir les exigences de ces systèmes exige une connaissance de l'environnement radiatif spatial et de ses effets sur les technologies électroniques et optoélectroniques, ainsi qu'une évaluation appropriée des risques liés aux incertitudes impliquées. Pour les missions à forts niveaux de rayonnement, des circuits intégrés résistants aux radiations seront nécessaires pour assurer les fonctions critiques de la mission. Les systèmes spatiaux les plus performants seront ceux qui sauront combiner l'électronique commerciale standard avec une électronique personnalisée résistante aux radiations, dans une combinaison adaptée au système étudié. Extrait d'un article de Peter S. Winokur, des Laboratoires nationaux de Sandia.